| USN |

|-----|

|-----|

10EC56

## Fifth Semester B.E. Degree Examination, June/July 2015 Fundamentals of CMOS VLSI

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, selecting atleast TWO questions from each part.

## PART - A

- Discuss the nMOS enhancement mode transistor for different conditions of yellow (06 Marks)

- Elaborate the concept of P-well falorication with neat sketches. (10 Marks)

- Compare CMOS and bipolar technologies.

(04 Marks)

- Obtain the transfer characteristics of a CMOS inverter and mark all the regions. Showing the status of PMOS and NMOS transistors. (10 Marks)

- b. Illustrate the schematic and stick diagram for the expression  $Y = \overline{A(B+C)}$ . (10 Marks)

- Discuss in detail the  $\lambda$  based design for CMOS. (10 Marks) Realize a 3-input NAND gate for clocked CMOS logic and also for CMOS domino logic.

- (06 Marks) Discuss the working of pseudo nMOS logic with suitable example. (04 Marks)

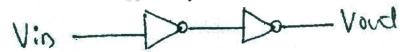

- a. Describe the delay unit  $\tau$  in terms of sheet resistance and area capacitance for the CMOS inverter pain shown, calculate the total delay. (08 Marks)

Fig. Q4(a)

b. Explain in brief the wiring capacitances.

(06 Marks)

- c. Narrate the steps involved in calculate the sheet resistance of :

- i) Transistor channel ii) nMOS inverter iii) CMOS inverter.

(06 Marks)

## PART - B.

- What are the scaling factors for the following device parameters:

- i) Gate capacitance cg ii) max-operating frequency f0 iii) current density iv) power dissipation per gate p<sub>g</sub> v) power speed product PT. (10 Marks)

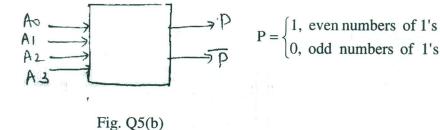

- Design a parity generator with the following specifications and draw the stick diagram of one basic cell.

(10 Marks)

## 10EC56

| 6 | a.<br>b.<br>c. | Draw the basic form of a two-phase clock generator and explain in detail. Discuss the architectural issues to be followed in the design of a VLSI subsystem. Explain the precharge bus approach used in system design. | (08 Marks)<br>(06 Marks)<br>(06 Marks) |

|---|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 7 | a.<br>b.       | Explain the three transistor dynamic RAM cell.  Discuss the Bangh-Wooley method used for two's complement multiplication.                                                                                              | (10 Marks)<br>(10 Marks)               |

| 8 | a.<br>b.<br>c. | Narrate the meaning of "Real Estate" in VLSI design. Explain testing and testability in detail. Write a short note on scan design techniques.                                                                          | (05 Marks)<br>(10 Marks)<br>(05 Marks) |

|   |                | *****                                                                                                                                                                                                                  |                                        |

|   |                | Narrate the meaning of "Real Estate" in VLSI design. Explain testing and testability in detail. Write a short note on scan design techniques.  *****  *****  *****  *****  ******  ****                                |                                        |