10ES32

## Third Semester B.E. Degree Examination, June/July 2015 **Analog Electronic Circuits**

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, selecting atleast TWO questions from each part.

## PART - A

- State and explain the various resistance levels of the semiconductor diode. (06 Marks)

- Explain the working of a full wave centre tapped rectifier. Also determine ripple factor, (10 Marks) efficiency and voltage regulation.

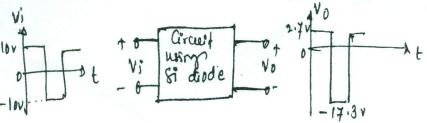

- c. Design a suitable circuit represented by the box shown below, which has the input and (04 Marks) output waveforms as indicated.

Fig. Q1(c)

- Name different biasing methods of transistor. With circuit diagram analyze the fixed bias 2 (10 Marks) circuit, with effect of variation in I<sub>B</sub>, R<sub>c</sub> and V<sub>CC</sub> on Q. point of the load line. (04 Marks)

- b. Explain the circuit of a transistor switch being used as an inverter.

- c. In a voltage divider bias circuit of BJT.  $V_{CC}=20~V,~R_{C}=10~k\Omega,~RE=1.5~k\Omega,$  $R_1=40~\text{k}\Omega$ ,  $R_2=4~\text{k}\Omega$ . Assume silicon transistor with  $\beta=150$ . Find  $I_C$ ,  $V_{CE}$  and  $I_{C(sat)}$  using (06 Marks) exact analysis.

- Define h parameters and hence derive h parameters model of CE BIT. (06 Marks)

- b. Explain with a neat circuit diagram of emitter follower configuration. Justify how voltage (06 Marks) gain is nearly equal to one.

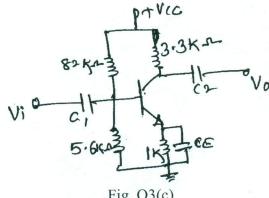

- For the circuit shown below determine  $V_{CC}$ , if  $A_V = -160$  and  $r_0 = 100$  k $\Omega$ . Take  $\beta = 100$ . (08 Marks)

Fig. Q3(c)

10ES32

- a. Draw the single stage RC coupled BJT amplifier and discuss the effect of (low frequency response): i) Input capacitance C<sub>S</sub> ii) output capacitance C<sub>C</sub> and iii) Emitter by pass (05 Marks) capacitance Ce on frequency response.

- b. Prove that miller effect of input capacitance  $C_{Mi} = (1 A_v)$  Cf and output capacitance

$C_{M0} = \left(1 - \frac{1}{A_v}\right) C_f.$ (10 Marks)

- c. It is desired that the voltage gain of an RC coupled amplifier at 60 Hz should not decrease by more than 10% from its mid bond value. Calculate:

- i) the lower 3 dB frequency

- ii) the required C if  $R = 2000 \Omega$ .

(05 Marks)

## PART - B

- a. Derive expressions for Z<sub>i</sub> and A<sub>i</sub> for a Darlington emitter follower circuit. (10 Marks)

- Mention the types of feedback connections. Draw their block diagrams indicating input and (06 Marks) output signal.

- c. List the general characteristics of a negative feedback amplifier and write its advantages.

(04 Marks)

- With a neat circuit diagram, explain the operation of a transformer coupled class A power 6 (07 Marks) amplifier.

- b. Explain the operation of a class B push-pull amplifier and derive its conversion efficiency. (08 Marks)

- The following distortion reading are available for a power amplifier:  $D_2 = 0.2$ ,  $D_3 = 0.02$ ,  $D_4 = 0.06$ , with  $I_1 = 3.3$ A and  $R_C = 4 \Omega$ . Calculate: i) the THD ii) the fundamental power component iii) the total power. (05 Marks)

- a. Explain the working of Wien bridge oscillator.

(07 Marks)

- b. With a neat circuit diagram, explain the operation of BJT Colpitts oscillator. (06 Marks)

- c. A crystal has the following parameter L=0.334 H,  $C_M=1$  pF, C=0.065 and R=5.5 k $\Omega$ . Calculate the series resonant frequency, parallel resonant frequency and find Q of the (07 Marks) crystal.

- Draw the JFET common drain configuration (source follower) circuit. Derive Zi, Z<sub>0</sub> and A<sub>v</sub> using small signal model. Write its characteristics. (10 Marks)

- b. Compare JFET and MOSFET.

(03 Marks)

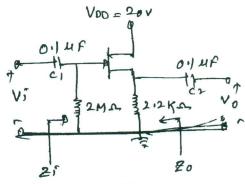

For the JFET common drain configuration shown below. Given  $I_{dss} = 10$  mA,  $V_P = -5V$ ,  $r_d = 40 \text{ k}\Omega$ ,  $V_{GSQ} = -2.85 \text{ V}$  i) Calculate  $Z_i$  and  $Z_0$  ii) Calculate  $A_v$  iii) find  $V_0$  if  $V_i = 20 \text{ mV}$ (07 Marks)

Fig. Q8(c)